基于可测试性的PCB元件布局优化策略与案例

来源:捷配链

时间: 2026/04/14 10:10:02

阅读: 23

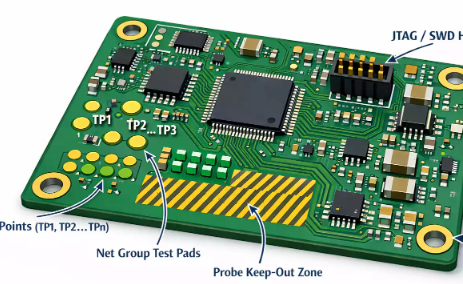

可测试性元件布局并非抽象理论,而是可落地、可执行、可验证的系统化设计方法。从布局前期规划、核心元件定位、功能分区规划、测试点协同布局到合规性检查,每一步都围绕 “可访问、可控制、可观测” 三大目标展开。本文结合消费电子、工业控制、汽车电子三大典型场景,提供可直接复用的布局策略、参数规范与实战案例,帮助工程师快速提升 PCB 可测试性。

一、可测试性元件布局的前期规划:源头规避风险

布局前完成 3 项核心规划,避免后期返工:

-

确定测试策略:明确测试类型(ICT/FCT/ 飞针)、覆盖率目标(≥95%)、测试面(优选单面)。

- 量产产品:ICT+FCT 组合,单面测试,覆盖率≥95%。

- 小批量 / 研发:飞针测试,双面兼容,覆盖率≥90%。

-

划分测试禁布区:

- 定位孔周围 3.2mm、板边 3mm、高大元件周围 5mm、连接器周围 2mm 为绝对禁布测试点区。

- 测试面高度上限 6mm,超过则布局在非测试面。

-

预留测试通道:

- 核心 IC(BGA/QFP)周围预留 1.5-2mm 扇出通道。

- 电源、地、时钟网络预留专用测试通道,宽度≥1mm。

二、分场景可测试性元件布局策略与参数规范

场景一:消费电子(手机 / 平板 / 智能家居)—— 高密度小型化

核心需求:板面积小(<100cm²)、双面贴片、高密度(线宽 / 线距 0.1mm)、量产 ICT 测试、高覆盖率。

布局策略:

-

核心 IC 布局

- BGA/QFN 布局在顶面(元件面),周围预留 2mm 扇出区,测试点全部引出至顶面空白区域。

- 同类型 IC 方向统一,间距≥0.8mm,测试点按 2.54mm 网格排列。

-

元件高度控制

- 顶面(测试面)元件高度≤3mm,电解电容、电感、电池座全部布局在底面。

- 底面元件高度≤2mm,避免与顶面测试点垂直重叠。

-

分立元件布局

- 去耦电容采用 0402 封装,紧贴 IC 电源引脚(<0.8mm),对称布局,预留 0.5mm 测试间隙。

- 电阻、电容按功能分组,整齐排列,间距≥0.5mm,测试点布置在元件外侧。

-

接口元件布局

- 连接器集中在单侧板边,预留 50% 板边作为测试区,测试点均匀分布在其余三边。

- 板边 3mm 内无高大元件,测试点距板边≥2mm。

参数规范:

- 测试点直径 1.0mm,间距≥1.27mm。

- 测试点与元件边缘≥1mm。

- 测试覆盖率≥95%,单面测试占比≥90%。

实战案例:某智能家居控制板(50mm×50mm,8 层)

- 优化前:BGA 周围无扇出区,高电容布局在测试面,测试覆盖率 65%,测试时间 180 秒。

- 优化后:BGA 预留 2mm 通道,高电容移至底面,测试点单面网格布局,覆盖率 92%,测试时间 45 秒,良率从 70% 升至 95%。

场景二:工业控制 PCB(PLC / 变频器 / 传感器)—— 高可靠高稳定

核心需求:宽温环境(-40℃~85℃)、高干扰、FCT+ICT 全测试、可维修性、长寿命。

布局策略:

-

功能分区布局

- 按电源、数字、模拟、接口四大功能分区,分区间距≥5mm,用地平面隔离。

- 每个分区独立设置测试点,模块间串联 0Ω 电阻,测试时可隔离独立测试。

-

关键元件布局

- 电源模块(LDO/DC-DC)集中布局,靠近板边,测试点集中在模块外侧。

- 晶振、运放、ADC 等敏感元件布局在无干扰区,远离电源、电感、继电器(间距≥5mm)。

- 高故障率元件(继电器、保险丝、端子)布局在板边易接触位置,方便返修复测。

-

测试安全布局

- 功率元件(MOS、IGBT)集中布局,远离测试密集区,测试点间距≥3mm。

- 测试点均匀分布,局部密度≤3 点 /cm²,避免 PCB 应力集中。

参数规范:

- 测试点直径 1.2mm,间距≥2.54mm。

- 测试点与功率元件间距≥3mm。

- 模块隔离测试点≥2 个 / 模块。

场景三:汽车电子(BMS/ECU/ 自动驾驶)—— 车规级高可靠

核心需求:AEC-Q100 认证、-40℃~125℃宽温、抗振动、高测试覆盖率、零缺陷。

布局策略:

-

全板可测布局

- 所有 IC(含 BGA)100% 引出测试点,电源 / 地网络每 2A 电流设置 1 个测试点。

- 测试点全部布局在顶面(焊接面),底面仅布置低矮元件(<1.5mm)。

-

抗振动布局

- 元件对称、均匀布局,重心居中,避免局部密集。

- 高大元件(电容、电感)采用加固布局,周围无测试点,支撑柱避开元件。

-

车规合规布局

- 测试点距板边≥5mm,距定位孔≥3.2mm。

- 所有测试点标注清晰丝印(TPxx),方便维修测试。

参数规范:

- 测试点直径≥1.0mm,间距≥1.5mm。

- 元件间距≥0.8mm,测试点与元件边缘≥1.5mm。

- 测试覆盖率 100%,车规级可靠性测试通过。

三、可测试性元件布局的关键技巧

-

测试点与元件协同设计

- 元件布局时同步确定测试点位置,避免先布元件后补测试点。

- 优先利用元件引脚(如插件元件引脚)作为测试点,减少专用测试点焊盘。

-

高密度板的 “微通道” 布局

- 0.5mm 间距 BGA 采用 “边缘扇出 + 微过孔”,将测试点引至外侧空白区。

- 采用 0201 小封装元件,释放测试空间,测试点密度提升 40%。

-

避免常见布局误区

- ? 误区:测试点布置在元件下方、高大元件阴影区、板边卡槽区。

- ? 误区:元件方向混乱、间距不均、测试点局部密集。

- ? 误区:双面测试点分散、底部元件过高、支撑点压在元件上。

四、可测试性布局检查清单(量产必备)

- 测试面元件高度是否≤6mm?

- 测试点与元件边缘间距是否≥1mm?

- 测试点是否 90% 以上集中在单面?

- 定位孔、板边、连接器禁布区是否合规?

- 核心 IC 是否预留扇出测试通道?

- 测试点是否均匀分布、无局部密集?

- 功能模块是否分区清晰、可独立测试?

- 高大元件是否集中在非测试面?

可测试性元件布局是设计与制造的 “桥梁”,直接决定产品量产效率与质量。通过场景化策略、标准化参数、实战化技巧,将可测试性融入布局全流程,不仅能破解测试难题、降低成本,更能提升产品可靠性与维修便利性,是现代 PCB 工程师必须掌握的核心技能。